随着网络通信技术的发展,芯片在军事、经济和社会中发挥着越来越重要的作用。分组密码[1]作为重要的加密算法,其高效实现直接影响系统的性能。可重构阵列密码处理器针对不同的加密算法进行优化,相比ASIC专用处理器,具有很高灵活性。近年来,面向分组密码可重构处理架构的研究也越来越多。因此,如何充分开发分组密码的并行性[2]和流水特性[3],如何设计高性能可重构分组密码处理架构,已经成为密码实现技术的重要研究问题之一。

国内外的研究者们对可重构分组密码的高效实现进行了研究。文献[4]提出了含有多Bank存储器的新型CGRA架构,数据被存储在多个Bank内,虽然提高了并行访问能力,但由于和本文需要处理的粗粒度位宽不匹配,因此未能充分达到并行的需求。文献[5]提出了可重构分簇式分组密码处理架构RCBCP,设计并实现了5级及运算单元内流水结构,提高了分组算法的加密性能。但复杂的可重构运算单元,使得关键路径较大,在一定程度上限制了系统的性能。文献[6]提出的Cryptoraptor阵列结构处理器,集成了80个PE处理单元,使得和DES算法在CBC模式下的吞吐率达到6.4 Gb/s和2.67 Gb/s,资源消耗巨大。

为充分挖掘分组密码的并行性和流水特性,本文首先提出了一种可重构多发射流水处理架构(Reconfigurable Multi-launch Pipeline Processing Architecture,RMPA)。设计该架构的目的在于减少闲置资源,从而提高可重构计算处理器的资源利用率和运算效率。此外,为了满足可重构阵列系统的高并行度特点,本文还提出了相应的多发射数据管理机制。高效的数据管理对于可重构阵列的处理性能有显著的提升。

1 RMPA-可重构多发射流水处理架构

可重构分组密码多发射流水处理架构RMPA是以PEs阵列为主要构成元素,结合流水线技术提出的。流水线结构是高效计算常采用的处理结构。通过分析分组密码的核心操作,并用流水结构进行处理,使得多个数据在流水线中并行开始不同的操作。该架构的基本思路是:利用具有32 bit粗粒度的n×n-PEs阵列来处理各种粒度的密码算法,并从中开发算法的深度流水和适度并行特性。

1.1 RMPA整体架构设计

RMPA整体架构如图1所示,可抽象分成3级:RU(Reconfigurable Unit)功能单元级、RE(Reconfigurable Element)阵列级和RMPA架构级。RU功能单元是提供密码操作功能的关键部件,在详细分析了分组密码算法运算单元的基础上,RU功能单元主要执行以下7种操作:S盒、GF(2n)乘法、移位、模乘、比特置换、逻辑和模加/减。每一个RU可以执行一个字级操作,能够满足分组密码的各种位宽,并且每个RE都附加了一个寄存器文件(Register file)和一个配置寄存器(Configuration Reg),寄存器文件用于寄存临时数据和中间结果。配置寄存器通过配置不同上下文,可以提高系统的处理性能。PE阵列是由n×n个REs通过Crossbar分层互连结构组成的。RMPA架构主要由主控制器(Main Controller)、配置上下文控制器(Context Controller)、RE阵列(Array)、主存储器(Main Memory)、Bank存储器(Bank Memory)和密钥存储器(Key Memory)构成。主控制器负责对整个系统进行控制。主存储器存储配置信息和数据,它会根据需求将数据输入到配置模块或Bank存储器中。Bank存储器则是存储待处理的数据和处理完的数据,且Bank存储器可以被RE阵列和DMA控制器访问,DMA控制器负责主存储器和Bank存储器之间进行数据交换。密钥存储器用于存储算法生成的子密钥。该结构采用动态模式配置上下文,每一个RE内部都有自己的配置寄存器,而且能够直接和配置上下文存储器连接。配置控制器从本地配置存储器选择正确的上下文,然后写进每一个REs的配置寄存器。

1.2 多总线互连网络结构

阵列中处理单元的行与列之间多采用总线、2D-Mesh和Crossbar互连结构。相比之下,虽然总线和2D-Mesh的代价较低,但在灵活性上与Crossbar相差甚远。为使并行处理更加高效地进行,同时降低互连网络的复杂度,本文在Crossbar网络的基础上采用多总线互连网络结构。

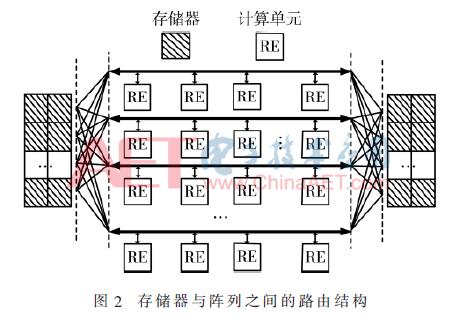

Bank存储器与阵列之间采用多总线互连网络结构,如图2所示。同一列上的RE需连接到一条总线上,任一列的总线可以连接到任何一个Bank上,这种互连网络能够保证每一个PE可以访问到任何一个Bank,任何一个Bank内的数据可以输入到功能单元中;每一层的数据可以进行隔层传输,处理完的数据或输出到Bank存储器或密钥存储器内。这种互连网络结构使该架构能够灵活支持CBC反馈模式的密码运算。

2 RMPA架构多发射机制

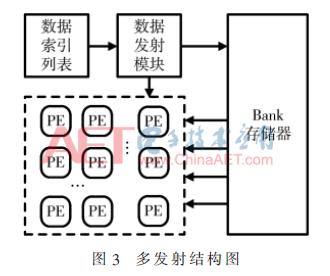

RMPA架构的多发射机制,原理就是使存储器往阵列中同时发射多组数据,进而有效提高系统的处理性能。为满足这一条件,不仅需要设计一种数据多发射结构,而且对存放数据的Bank也有一定的要求。多发射结构如图3所示,主要由数据分发模块和数据索引列表组成。数据分发模块的作用在于确保可重构阵列中数据的流水实现;数据索引列表则对数据包进行区分,以保障数据包的完整性。

2.1 RAM存储结构

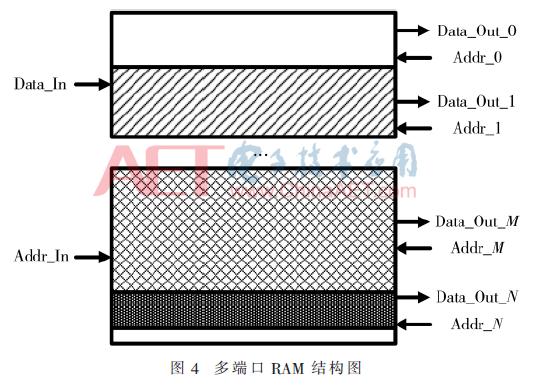

基于多发射研究,考虑如何实现数据包存储资源的动态分配[7],从而降低硬件资源的浪费和吞吐率的提升。RAM作为重要的Bank组成结构,主要用于实现对数据的缓存,不同于FIFO结构的数据输入输出过程,RAM依靠地址实现对数据的写入与读出,数据读出顺序与其写入顺序无关。因此,构建了图4所示的多端口RAM结构。

采用多输出RAM结构构建了数据存储的基础,通过地址选择输出数据的来源。由于RAM地址是连续的,因此在数据存储时可以确保数据的连续存储,通过地址来区分不同的数据包,使数据包的注入更加灵活。为了满足对不同长度数据包的并行注入及下一数据包的动态加载,下面将针对数据发射模块的结构展开详细研究。

2.2 数据发射模块结构及索引列表

数据发射模块是确保可重构阵列流水实现的基础,根据上一节对数据存储模块的研究可知,数据存储模块采用多输出RAM结构实现。同时,由于不同数据包的长度不同,因此数据发射模块需要具备独立并行处理数据的特征,从而降低因数据包长度的差异导致的流水线中断的情况发生。

在数据存储模块中,不同的数据包依靠数据包的起始地址及数据包长度进行区分。在数据发射模块中,需要支持数据读取的起始地址和长度可以动态配置。因此,构建了图5所示的数据发射模块的基本结构。

起始寄存器用于存储数据包的起始地址(基地址),可配置计数器用于产生当前数据包中数据的偏移地址,通过加法器将基地址与偏移地址相加可以得到当前送往可重构阵列的数据地址。配置控制模块用于读取数据包包头并对包头进行解析,得到当前数据包的起始地址及长度,以实现对起始寄存器及可配置寄存器的配置。同时,配置控制模块也会产生数据存储模块的读使能,与数据地址相配合,从数据存储模块中读取相应的数据并送入可重构阵列中相应的位置。

为了确保数据包的完整性以及数据包在数据存储模块中存储的齐整性,本文构建了基于任务映射的数据包索引机制,并在多发射结构中增加了共享的数据包索引列表,用于实现对数据包的索引。为了对数据包进行区分,本文构建了基于任务号及数据包包号的数据索引列表,其格式定义如图6所示。

为便于存储,本文将数据包索引列表定义为32 bit。其中第28到31 bit代表任务编号,用于对不同的任务进行区分,共4 bit,能够支持最大16个任务;第26到27 bit为保留字段;第20到25 bit为数据包包号,用于区分同一任务中的不同数据包,共6 bit,因此单任务能够支持最大64个数据包;对于网络数据包而言,其长度在64~1 518 B范围,因此定义1 518 B为单个数据包的最大长度,则可以采用9 bit表示单个数据包的长度,最大支持2 048 B的数据;由于本文采用多路并行结构设计数据发射模块,在数据存储模块中应至少能够容纳多组最大长度的数据包,因此本文将起始地址长度定义为11 bit,从而满足应用需求。

2.3 数据多发射接口电路设计

数据输入接口电路结构如图7所示。上位机将待加解密应用分解为不同的任务,并对每个任务中的数据进行划分,划分为不同长度的数据包。根据数据包索引列表格式建立数据包索引列表,将数据包存入数据存储模块中的相应地址。当应用被确定后,各数据包的起始地址即被确定,为了尽可能减少存储资源消耗,采用数据覆盖的方式在数据存储模块中对数据包进行存储,当某一数据包完成运算后,其所占用的存储资源即被释放,可以在相应存储资源上进行覆盖存储。这一过程主要由上位机实现,通过对数据包运算过程的规划,实现数据的无冲突读写。

输入数据接口的工作流程如下:

(1)数据发射模块从数据包索引列表中分别读取数据包索引,并解析数据包索引中的数据包起始地址及长度,将数据包起始地址写入起始寄存器,并将可配置计数器的溢出值设置为数据包长度;

(2)数据发射模块生成数据包的读地址及读使能,并将相应信号送至数据存储模块;

(3)数据存储模块依据地址及读使能,将相应数据取出并输出至粗粒度可重构阵列的对应位置,同时,配置控制模块生成相应的写使能;

(4)当数据发射模块中可配置计数器产生溢出时,生成溢出信号并传递至配置控制模块,配置控制模块按顺序从数据包索引列表中读取数据包索引,继续进行运算。

输入数据接口的工作流程确保了输入数据接口能正确地实现数据包的解析、数据的读取及发射,确保了粗粒度可重构阵列中流水线的连续正确运转。

3 实现性能比较

本设计采用Verilog硬件描述语言对分组密码算法进行RTL级描述,利用QuartusⅡ9.0软件工具对设计进行时序仿真,并选用65 nm CMOS工艺标准单元库逻辑综合获得硬件资源代价。验证环境使用Synopsys公司的DC(Design Compiler)逻辑综合工具,它可以将硬件设计代码转换为门级网表,并且能够映射为特定工艺下的标准单元。为保证工作稳定性,将RMPA的工作频率设置为350 MHz,根据仿真综合结果,为更加全面地评估RMPA的实现性能,本文选取典型分组密码算法AES进行分析。RMPA与其他可重构结构性能对比情况如表1所示。其中RCBCP[5]和Cryptonite[8]为专用指令密码处理器,Celator[9]、RCPA[10]和S-RCCPA[11]为可重构阵列密码处理结构。由于各处理结构采用的工艺有较大差异,因此将各结构的面积和吞吐率均按照65 nm CMOS工艺换算并进行比较。

结果表明,RMPA多发射结构可以高效处理AES分组密码算法,且吞吐率明显高于其他专用指令处理器。与Celator和BCORE等其他可重构阵列结构相比较,本结构对分组密码算法的吞吐率仍处于优势。

4 结论

为充分挖掘分组密码在可重构阵列中的流水及并行特性,本论文提出了一种面向分组密码的可重构多发射流水处理架构RMPA。在65 nm CMOS工艺下对RMPA进行了逻辑综合和功能仿真,分析了AES算法在该架构下的加密性能,其单发射/多发射吞吐率分别达到了0.9 Gb/s和3.19 Gb/s。相比其他密码处理器,本架构吞吐率高,有一定的性能优势,具有更好的应用前景。下一步将根据需求对数据的多收集机制进行研究,并采用多种分组密码算法进行分析比较,完善该架构体系。