什么是FIFO?

FIFO一般用于不同时钟域之间的数据传输,也常用来实现不同位宽的接口的数据匹配。

- “不同时钟域间传输数据”时,FIFO类似缓存,根据时钟A,向FIFO中写入数据,根据时钟B,读取FIFO数据。

- “不同位宽传输数据”时,FIFO同样类似缓存,将FIFO接收配置为8位数据,输出配置为16位数据。FIFO接收到的8位数组,按照高低组合为16位数据进行输出。

配置FIFO的ip核

参考:如何创建使用IP核-PPL?

在“菜单栏 - Tools - MegaWizard Plug-In Manage”创建“FIFO”核。

- 位宽与时钟配置

输入与输出均为8字节宽度,有256个字的缓存深度,输入与输出为不同时钟。

- DCFIFO1(FIFO优化,平衡性能与资源消耗)

- DCFIFO2(控制标志信号)

“full”:表示缓存满“empty”:表示缓存空“usedw”:可被读取的缓存容量

- 读请求模式、Blk类型

正常模式:数据正常被读取

前显模式:相比较正常模式前移一字节,导致处于读取状态下,实际读取的是第二个数据。

- 电路保护等选项

电路保护使用默认选项,不勾选即为开启电路保护。资源使用默认选项,使用FIFO中自带的存储资源 - 仿真

altera_mf文件,提供仿真功能。

- summary总结界面

勾选后,可生产对应的文件。需要“fifo_inst.v”例化文件

- 例化

在工程文件夹下“paripcore”中的“fifo_inst.v”为例化文件,可在顶层文件中使用此例化,替换传参即可。

移植到顶层文件中

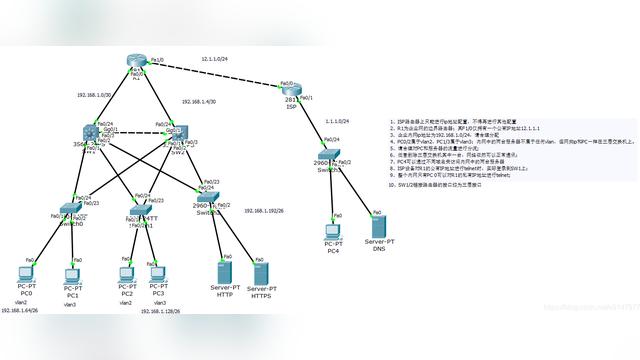

工程配置

工程框架:

通过写模块,向FIFO中写入数据;

通过读模块,从FIFO中获取数据;

- 顶层文件

分别例化fifo的ip核、读模块、写模块

- 读模块

通过状态机形式,默认处于“等待读取”状态,先检查是否存在读满信号,存在则进入“允许读取”状态;在“允许读取”状态下,判断是否存在读空信号,若存在读空信号,进入“等待读取”,若不存在读空信号,持续读取。

- 写模块

同样通过状态机的形式进行。默认“等待写空”

- 验证

编译后,通过“SignalTap”进行验证。

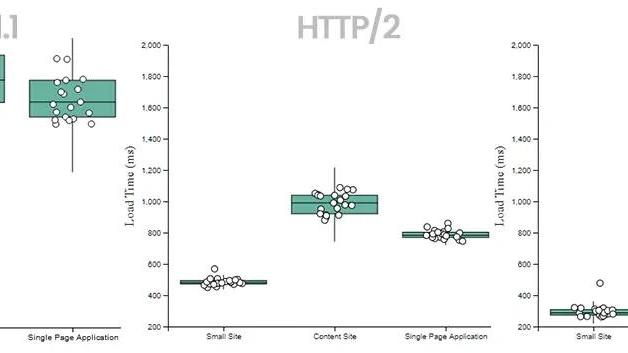

波形变化,可以观察到从读数据到写数据的变化情况

之前配置fifo的ip核时,设置256字,故显示0-255。

再修改为128字,则结果如下: